1. Krishna Kant, "Microprocessor and Microcontrollers", Eastern Company Edition, Prentice Hall of India, New Delhi, 2007.

2. R.S. Gaonkar, 'Microprocessor Architecture Programming and Application', with 8085, Wiley Eastern Ltd., New Delhi, 2013.

3. Soumitra Kumar Mandal, Microprocessor & Microcontroller Architecture, Programming & Interfacing using 8085,8086,8051,McGraw Hill Edu,2013.

#### **REFERENCES:**

1. Muhammad Ali Mazidi & Janice Gilli Mazidi, R.D.Kinely 'The 8051 Micro Controller and Embedded Systems', PHI Pearson Education, 5th Indian reprint, 2003.

2. N.Senthil Kumar, M.Saravanan, S.Jeevananthan, 'Microprocessors and Microcontrollers', Oxford, 2013. 3. Valder – Perez, "Microcontroller – Fundamentals and Applications with Pic," Yeesdee Publishers, Tayler & Francis, 2013.

Prepared By

1. Mrs.J.Srivandhana., AP/MCA 2. Mrs.T.Kala., AP/MCA

Verified By

Τ

#### PART A

#### 1. What is a microcomputer?

A computer that is designed using a microprocessor as its CPU is called microcomputer.

#### 2. What is Microprocessor? Give the power supply & clock frequency of 8085.

A microprocessor is a <u>multipurpose, programmable logic device</u> that reads binary instructions from a storage device called <u>memory</u>. Accepts binary data as <u>input</u> and <u>processes</u> data according to those instructions and provides result as <u>output</u>. The power supply of 8085 is +5V and clock frequency in 3MHz.

Microprocessor is a programmable integrated device that has computing and decisionmaking capability similar to that of the Central Processing Unit (CPU) of a computer.

#### 3. List the components of microprocessor (single board microcomputer) based system

The microprocessor based system consist of microprocessor as <u>CPU</u>, <u>semiconductor</u> <u>memories like EPROM and RAM</u>, input device, output device and interfacing devices.

#### 4. What are the basic units of a microprocessor?

The basic units or blocks of a microprocessor are <u>ALU</u>, an <u>array of registers</u> and <u>control</u> <u>unit</u>.

#### 5. List few applications of microprocessor-based system.

It is used:

- For measurements, display and control of current, voltage, temperature, pressure, etc.

- For traffic control and industrial tool control.

- For speed control of machines.

#### 6. Define bit, byte and word.

A <u>digit of the binary number</u> or code is called bit. Also, the bit is the fundamental storage unit of computer memory.

The 8-bit (8-digit) binary number or code is called **byte** and 16-bit binary number or code is called **word.** (Some microprocessor manufactures refer the basic data size operated by the processor as word).

### 7.Specify the size of data, address, and memory word and memory capacity of 8085 microprocessor. (*April/May-2011*)

8085 has data lines (D<sub>0</sub>-D<sub>7</sub>) 16 address lines (A<sub>0</sub>-A<sub>15</sub>) Memory capacity =  $2^{16}$  = 64 k Bytes of memory.

#### 8. What are the functions of an accumulator?[Apr/May 2018]

The accumulator is the register associated with the ALU operations and sometimes I/O operations. It is an integral part of ALU. It holds one of data to be processed by ALU. It also temporarily stores the result of the operation performed by the ALU.

#### 9. List the 16 – bit registers of 8085 microprocessor.

Stack pointer (SP) and Program counter (PC).

#### 10. List the allowed register pairs of 8085.

- B-C register pair

- D-E register pair

- H-L register pair

#### 11. Mention the purpose of SID and SOD lines.

• SID (Serial input data line):

It is an input line through which the microprocessor accepts serial

data. • SOD (Serial output data line):

It is an output line through which the microprocessor sends output serial data.

#### 12. What happens to the 8085 processor when it is resetted?

When the 8085 processor is resetted it executes the first instruction at the OOOOH location. The 8085 resets (clears) instruction register, interrupt mask bits and other registers.

#### 13. What is an Opcode and Operand?

The part of the instruction that specifies the operation to be performed is called the operation code or opcode.

The data on which the operation is to be performed is called as an Operand.

#### 14. What is the function of IO/ signal in the 8085?

It is a status signal. It is used to differentiate between memory locations and I/O operations. When this signal is low (IO/ = 0) it denotes the memory related operations. When this signal is high (IO/ = 1) it denotes an I/O operation.

#### 15. How many address lines in a 4096 x 8 EPROM CHIP?

12 address lines.

#### 16. What is meant by polling?

Polling or device polling is a process which identifies the device that has interrupted the microprocessor.

#### 17. What is meant by interrupt?

Interrupt is an external signal that causes a microprocessor to jump to a specific subroutine.

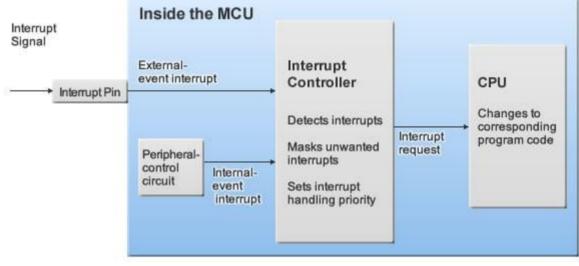

**Definition:** The meaning of 'interrupts' is to break the sequence of operation. While the cpu is executing a program, on 'interrupt' breaks the normal sequence of execution of instructions, diverts its execution to some other program called Interrupt Service Routine (ISR). After executing ISR, the control is transferred back again to the main program. Interrupt processing is an alternative to polling.

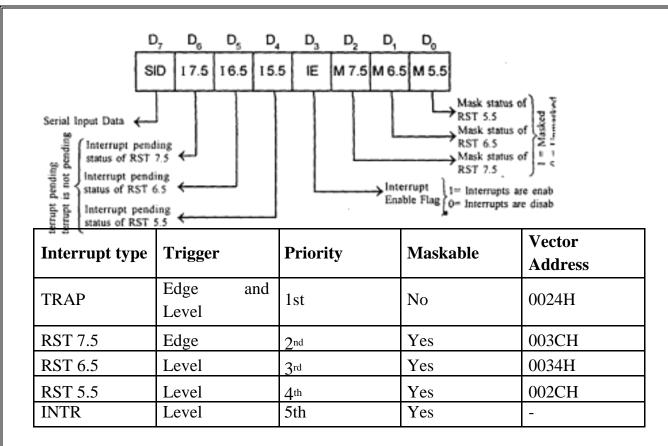

## 18. Explain priority interrupts of 8085. How many interrupts does 8085 have, mention them.[Nov/Dec 2017]

The 8085 microprocessor has five interrupt inputs. They are TRAP, RST 7.5, RST 6.5, RST 5.5 and INTR. These interrupts have a fixed priority of interrupt service. If two or more interrupts go high at the same time, the 8085 will service them on priority basis.

| Interrupts | Priority |

|------------|----------|

| TRAP       | 1        |

| RST 7.5    | 2        |

| RST 6.5    | 3        |

| RST 5.5    | 4        |

| INTR       | 5        |

#### 19. What is the signal classification of 8085?

All the signals of 8085 can be classified into 6 groups

- Address bus

- Data bus

- Control and status signals

- Power supply and frequency signals

- Externally initiated signals

- Serial I/O ports

## 20. How clock signals are generated in 8085 and what is the frequency of the internal clock? (*May/June-14*)

The 8085 has the clock generation circuit on the chip but an external quartz crystal or L C circuit or RC circuit should be connected at the pins XI and X2. The maximum internal clock frequency of 8085A is 3.03 MHz

#### 21. What are operations performed on data in 8085

The various operations performed are

- Store 8-bit data

- Perform arithmetic and logical operations

- Test for conditions

- Sequence the execution of instructions

- Store data temporarily during execution in the defined R/W memory locations called the stack

#### 22. List the steps involved to fetch a byte in 8085?

- The PC places the 16-bit memory address on the address bus

- The control unit sends the control signal RD to enable the memory chip

- The byte from the memory location is placed on the data bus

- The byte is placed in the instruction decoder of the microprocessor and the task is carried out according to the instruction

#### 23. What is meant by wait state?

This state is used by slow peripheral devices. The peripheral devices can transfer the data to or from the microprocessor by using READY input line. The microprocessor remains in the wait state as long as READY line is low. During the wait state, the contents of the address, address/data and control buses are held constant.

#### 24. What do you mean by multiplexing the bus?

The signal lines AD7-AD0 is bidirectional. They are used as the lowered address bus as well as the data bus. In executing the instructions, during the earlier part of the cycle, these lines are used as the low order address bus. During the later part of the cycle, these lines are used as the data bus. This is known as multiplexing the bus,

#### 25. Where is the READY signal used?

READY is an input signal to the processor, used by the memory or I/O devices to get extra time for data transfer or to introduce wait states in the bus cycles.

#### 26. List the control and status signals of 8085 microprocessor and mention its need.

#### (Nov/Dec-2012)

There are two control signal (RD and WR), three status signals ( IO/M, S1, S0). They are used to identify the basic type of internal operation done by the processor.

#### 27. What are HOLD and HLDA and how it is used?

Hold and hold acknowledge signals are used for the Direct Memory Access (DMA) type of data transfer. The DMA controller place a high on HOLD pins in order to take control of the system bus. The HOLD request is acknowledged by the 8085 by driving all its tri-stated pins to high impedance state and asserting HLDA signal high.

#### 28. Basic concepts in memory interfacing

The primary function of memory interfacing is that the microprocessor should be able to read from and write into a given register of a memory chip.

#### 29. Why interfacing is needed for I/O devices?

Generally I/O devices are slow devices. Therefore the speed of I/O devices does not match with the speed of microprocessor. And so an interface is provided between system bus and I/O devices.

#### 30. What is the drawback in memory mapped I/O?

When I/O devices are memory mapped, some of the addresses are allotted to I/O devices and so the full address space cannot be used for addressing memory (i.e., physical memory address space will be reduced). Hence memory mapping is useful only for small systems, where the memory requirement is less.

#### 31. What does memory-mapping mean?

The memory mapping is the process of interfacing memories to microprocessor and allocating addresses to each memory locations.

## **32.** How the 8085 processor differentiates a memory access (read/write) and I/O access (read/write)?

The memory access and I/O access is differentiated using 10 I M signal.

The 8085 processor asserts 10 IM low for memory read/write operation and 10 I M is asserted high for 1/0 read/write operation.

#### 33. What is the need for system clock and how it is generated in 8085?

The system clock is necessary for synchronizing various internal operations or devices in the microprocessor and to synchronize the microprocessor with other peripherals in the system.

#### 34. Why EPROM is mapped at the beginning of memory space in 8085system?

In 8085 microprocessor, after a reset, the program counter will have OOOOH address. If the monitor program is stored from this address then after a reset, it will be executed automatically. The monitor program is a permanent program and stored in EPROM memory.

If EPROM memory is mapped at the beginning of memory space, i.e., at OOOOH, then the monitor program will be executed automatically after a reset.

#### 35. What is the need for timing diagram? (April/May-15)

The timing diagram provides information regarding the status of various signals, when a machine cycle is executed. The knowledge of timing diagram is essential for system designer to select matched peripheral devices like memories, latches, ports, etc., to form a microprocessor system.

## 36. What is Instruction cycle & machine cycle? How many machine cycles constitute one instruction cycle in 8085?

### Instruction cycle

The sequence of operations that a processor has to carry out while executing the instructions is called as Instruction cycle. Each instruction cycle of a processor indium consists of a number of machine cycles.

#### Machine cycle

Machine cycle is defined as the time required to complete one operation of accessing memory, I/O, or acknowledging an external request. This cycle may consist of three to six T-states.

Each instruction of the 8085 processor consists of <u>one to five machine</u> cycles.

#### 37. What is processor cycle (Machine cycle)?

The processor cycle or machine cycle is the basic operation performed by the processor. To execute an instruction, the processor will run one or more machine cycles in a particular order.

#### 38. Define T-State.

T-State is defined as one subdivision of the operation performed in one clock period. These subdivisions are internal states synchronized with the system clock, and each T-State is precisely equal to one clock period.

#### 39. What is fetch and execute cycle?

In general, the instruction cycle of an instruction can be divided into fetch and execute cycles. The fetch cycle is executed to fetch the opcode from memory. The execute cycle is executed to decode the instruction and to perform the work instructed by the instruction.

#### 40. What is opcode fetch cycle?

The opcode fetch cycle is a machine cycle executed to fetch the opcode of an instruction stored in memory. Every instruction starts with opcode fetch machine cycle.

#### 41. What operation is performed during first T -state of every machine cycle in 8085?

In 8085, during the first T -state of every machine cycle the low byte address is latched into an external latch using ALE signal.

#### 42. What is ALE signal and READY signal? (Nov/Dec-09) (Nov/Dec-14)

The ALE (Address Latch Enable) is a signal used to de-multiplex the address and data lines, using an external latch. It is used to enable the external latch.

The READY signal of the 8085 microprocessor is sampled approximately one half clocks after the trailing edge of ALE and if not asserted, repeatedly one full clock cycle later until it is asserted.

#### 43. What is the use of ALE?(OR)Mention the use of ALE. (Nov/Dec-14)( Nov/Dec-15)

Prepared By: Mrs.J.SRIVANDHANA., AP/MCA & Mrs.T.Kala., AP/MCA

The ALE is used to latch the lower order address so that it can be available in T2 and T3 and used for identifying the memory address. During T1 the ALE goes high, the latch is transparent, and the output changes according to the input data, so the output of the latch is the lower order address. When ALE goes low the lower order address is latched until the next ALE.

#### 44. How many machine cycles does 8085 have, mention them

The 8085 have seven machine cycles. They are

- Opcode fetch

- Memory read

- Memory write

- I/O read

- I/O write

- Interrupt acknowledge

- Bus idle

#### 45. Why status signals are provided in microprocessor?

The status signals can be used by the system designer to track the internal operations of the processor. Also, it can be used for memory expansion (by providing separate memory banks for program & data and selecting the bank using status signals).

#### 46. Give the register organization of 8085

| W (8) Temp. Reg      | Z (8) Temp. Reg |  |  |  |  |  |  |  |

|----------------------|-----------------|--|--|--|--|--|--|--|

| B (8) Register       | C (8) Register  |  |  |  |  |  |  |  |

| D (8) Register       | E (8) Register  |  |  |  |  |  |  |  |

| H (8) Register       | L(8) Register   |  |  |  |  |  |  |  |

| Stack Pointer (16)   |                 |  |  |  |  |  |  |  |

| Program Counter (16) |                 |  |  |  |  |  |  |  |

#### 47. What is interrupt I/O?

If the I/O devices initiate the data transfer through interrupt then the I/O is called interrupt driven I/O.

#### 48. When the 8085 processor checks for an interrupt?

In the second T -state of the last machine cycle of every instruction, the 8085 processor checks whether an interrupt request is made or not.

#### 49. What is interrupt acknowledge cycle?

The interrupt acknowledge cycle is a machine cycle executed by 8085 processor to get the address of the interrupt service routine in-order to service the interrupt device.

#### 50. How the interrupts are affected by system reset?

Whenever the processor or system is resetted, all the interrupts except TRAP are disabled. In order to enable the interrupts, El instruction has to be executed after a reset.

#### 51. What is Software interrupts?

The Software interrupts are program instructions. These instructions are inserted at desired locations in a program. While running a program, if software interrupt instruction is encountered then the processor executes an interrupt service routine.

#### 52. What is TRAP? (May/June -2012)

The TRAP is non-Maskable interrupt of 8085. It is not disabled by processor reset.

#### 53. What is the difference between Hardware and Software interrupt?

The Software interrupt is initiated by the main program, but the Hardware interrupt is initiated by an external device. In 8085, the Software interrupt cannot be disabled or masked but the Hardware interrupt except TRAP can be disabled or masked

#### 54. What is vectored and Non- Vectored interrupt?

When an interrupt is accepted, if the processor control branches to a specific address defined by the manufacturer then the interrupt is called vectored interrupt. In Non-vectored interrupt there is no specific address for storing the interrupt service routine. Hence the interrupted device should give the address of the interrupt service routine.

#### 55. List the Software and Hardware interrupts of 8085?

Software interrupts: RST 0, RST1, RST 2, RST 3, RST 4, RST 5, RST 6 and RST 7. Hardware interrupts: TRAP, RST 7.5, RST 6.5, RST 5.5 and INTR.

or after reorganization of interrupt.

#### 56. What is masking and why it is required?

Masking is preventing the interrupt from disturbing the current program execution. When the processor is performing an important job (process) and if the process should not be interrupted then all the interrupts should be masked or disabled. In processor with multiple 'interrupts, the lower priority interrupt can be masked so as to prevent it from interrupting, the execution of interrupt service routine of higher priority interrupt.

#### 57. When the 8085 processor accept hardware interrupt?

The processor keeps on checking the interrupt pins at the second T-state of last Machine cycle of every instruction. If the processor finds a valid interrupt signal and if the interrupt is unmasked and enabled then the processor accepts the interrupt. The acceptance of the interrupt is acknowledged by sending an OOA signal to the interrupted device.

#### 58. When the 8085 processor will disable the interrupt system?

The interrupts of 8085 except TRAP are disabled after anyone of the following operations

• Executing El instruction.

- System or processor reset.

- After reorganization (acceptance) of an interrupt

#### 59. How the vector address is generated for the INTR interrupt of 8085?

For the interrupt INTR, the interrupting device has to place either RST opcode or CALL opcode followed by l6-bit address. IRST opcode is placed then the corresponding vector address is generated by the processor. In case of CALL opcode the given l6-bit address will be the vector address.

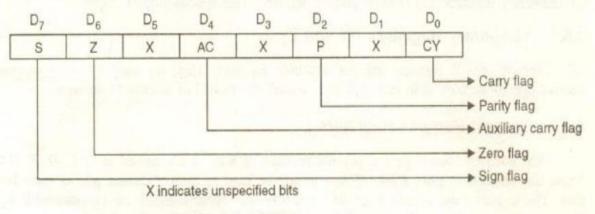

#### 60. Define Flags of 8085? (*May/June-14*)[Nov/Dec 2017]

The different flags and their positions in flag register are as shown in Fig. 4.6.

Fig. 4.6 : 8085 flag register

The flag register in the 8085 microprocessor.

- The flag register in 8085 is an 8-bit register which contains 5 bit positions.

- These five flags are of 1bit F/F and are known as zero, sign, carry, parity and auxiliary carry.

- For **sign flag** if the result of an MSB operation is 1 then it is set else it is reset.

- The **zero flag** is set of the result of an instruction is zero.

- The **auxiliary carry flag** is used for BCD operations, not free to the programmer.

- The carry flag is used for carrying and borrowing in case of addition and subtraction operations.

- The **parity flag** is used for results containing an even number of one's.

#### 61. Difference between memory mapped I/O and peripheral I/O? [Apr/May 2018]

| * <b>*</b>                                                          |                                                                                     |

|---------------------------------------------------------------------|-------------------------------------------------------------------------------------|

| MEMORY MAPPEED I/O                                                  | PERIPHERAL I/O                                                                      |

| 16-bit device address                                               | 8-bit device address                                                                |

| The data transfer between any general-purpose register and I/O port | The data transfer only between accumulator and I/O port                             |

| The memory map(64kb)is shared between I/O device and system memory  | The I/O map is independent of the memory map,256 input device and 256 output device |

| More hardware is required to decode 16-bit address                  | Less hardware is required to decode 8-bit address                                   |

#### 62. Define the functions of parity flag and zero flag in 8085? (May/June-2012)

Zero flag: if result is 0 than it is set condition i.e.1 otherwise it is reset i.e. is 0.

Parity flag: if number of 1's in the answer is even than it is set condition i.e.1 otherwise it is reset i.e. is 0.

#### 63. What is the use of Stack Pointer(SP)? (Nov/Dec-2015)

**Stack Pointer (SP):** The stack is a reserved area of the memory in the RAM where temporary information may be stored. A 16-bit stack pointer is used to hold the address of the most recent stack entry.

64. Write an 8085 assembly program to add two digit BCD numbers in memory locations 5000H and 5001H and store the result in memory location 5002H.(Nov 2016)

MOV A, 5000H INR A ADD E DAA STA 2300H MOV A, H ADC D DAA STA 2301H HLT

#### 65. List out the machine cycles for executing the instruction MVI A,34 H (Nov -16)

This is a 2 byte instruction so it requires 2 machine cycles to fetch the instruction

#### 1. Op code fetch and 2. Memory read

#### 66. Why data bus is bi-directional? (Apr/May -17)

The data bus is bidirectional because it takes the data from peripherals & also give the data to peripherals.

#### 67. List out the machine cycles of 8085 microprocessor.(Apr/May -17)

The 8085 microprocessor has seven basic machine cycles. They are

- Opcode fetch cycle (4T)

- Memory read cycle (3 T)

- Memory write cycle (3 T)

- I/O read cycle (3 T)

- I/O write cycle (3 T)

- Interrupt acknowledge cycle

- Bus idle cycle

#### 68. List out the uses of Microprocessors?

- 1. Calculators

- 2. Accounting system

- 3. Games machine

- 4. Complex Industrial Controllers

- 5. Traffic light Control

- 6. Data acquisition systems

- 7. Multi user, multi-function environments

- 8. Military applications

- 9. Communication systems.

#### 69) List out the Advantages of Microprocessor.

- Computational/Processing speed is high & Simplifies system design

- $\clubsuit$  Intelligence has been brought to systems

- $\clubsuit$  Automation of industrial process and office automation

- ✿ Flexible.

- Compact in size.

- **A**Maintenance is easier.

#### 70) Why address bus of Intel 8085 is unidirectional and data bus is bidirectional? [Apr/May 2016]

#### Why address bus is unidirectional?

The address is an identification number used by the microprocessor to identify or access a memory location or I / O device. It is an output signal from the processor. Hence the address bus is unidirectional.

#### Why data bus is bi-directional?

The microprocessor has to fetch (read) the data from memory or input device for processing and after processing, it has to store (write) the data to memory or output device. Hence the data bus is bi-directional.

#### 71) What is the function of NOP instruction in 8085.

NOP operation in 8085 is used to insert a delay of 4 T-states when microprocessor is communicating with slow peripheral devices. When enabling interrupts via the EI instruction, the interrupts are enabled after the successful execution of the next instruction.

#### 72) What is a stack pointer register, describe briefly.

-The Stack pointer is a sixteen bit register used to point at the stack.

- In read write memory the locations at which temporary data and return addresses are stored is known as the stack.

- In simple words stack acts like an auto decrement facility in the system.

- The initialization of the stack top is done with the help of an instruction LXI SP.

- In order to avoid program crashes a program should always be written at one end and initialized at the other.

#### 73) What is the use of DAD and DAA instruction in 8085 microprocessor? [Apr/May 2016]

The DAD instruction (Double Add) allows 16-bit addition between the HL register pair and any one of the BC, DE, HL, or SP register pairs, putting the result in HL. It takes a single operand which may be B, D, H, or SP. The carry flag is set to indicate overflow.

The DAA instruction (Decimal Adjust Accumulator) allows conversion of the 8-bit accumulator value to Binary Coded Decimal (BCD). If the low-order 4 bits of the accumulator are greater than 9, or the auxiliary carry flag is set, 6 is added to the low-order 4 bits of accumulator, then if the high-order 4 bits of the accumulator are greater than 9, or the carry flag is set, 6 is added to the high-order 4 bits of the accumulator.

#### 74) What differences can you state between the HLT and HOLD states?

- The Hold is a hardware input whereas HLT is a software instruction.

- When the HLT state is executed the processor simply stops and the buses are driven to tri state. No form of acknowledgement signal is given out by the processor.

- In case of HOLD the processor goes into hold state but the buses are not driven to tri state.

- When the processor goes into the HOLD state it gives out an HLDA signal. This signal can be made to use by other devices.

#### 75) Differentiate between 8085 and 8086 processors.

| 8085                                     | 8086                                      |

|------------------------------------------|-------------------------------------------|

| 8 bit microprocessor                     | 16-bit microprocessor                     |

| 16-bit address bus                       | 20-bit address bus                        |

| General purpose regi. Size are of 8 -bit | General purpose regi. Size are of 16 -bit |

| Instruction queue is not present         | 6 byte Instruction queue is present       |

| Segmentation is not supported            | Segmentation of memory is supported       |

| Doses not support pipeline architecture  | support pipeline architecture             |

| Maximum clock frequency is 3MHz          | Maximum clock frequency is 8MHz           |

|                                          |                                           |

#### PART B

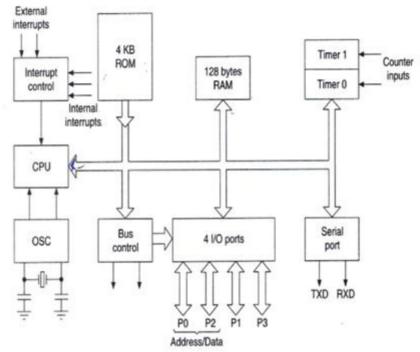

#### 1. List out the features of 8085 microprocessor.

The features of Intel 8085 microprocessor are as follows:

1) 8085 microprocessor is an 8 bit microprocessor. I.e. it can accept or provide 8 bit data simultaneously.

- 2) 8085 microprocessor is a single chip, NMOS device implemented with 6200 transistors.

- 3) 8085 microprocessor requires a single +5V <u>DC power</u> supply.

- 4) 8085 microprocessor provides on chip clock generator, therefore there is no need of external clock generator, but it requires external tuned circuit like LC, RC or crystal.

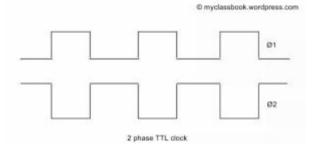

5) 8085 microprocessor requires two phase, 50% duty cycle, TTL clock. These clock signals are generated by an internal clock generator (refer following figure).

#### 2 Phase TTL clock

6) The maximum clock frequency of 8085 microprocessor is 3MHz where as minimum clock frequency is 500 KHz.

7) 8085 provides 74 instructions with the following addressing modes:

- register

- direct

- immediate

- indirect

- implied.

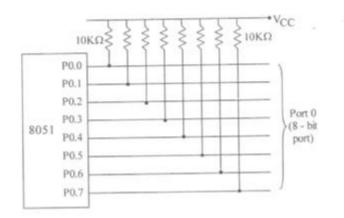

8) The data bus is multiplexed with the address bus, hence it requires external hardware to separate data lines from address lines (this is one of the disadvantage of 8085).

9) 8085 microprocessor provides 16 address lines, therefore it can access  $2^{16} = 64$ K bytes of memory.

10) It generates 8 bit I/O address, hence it can access  $2^8 = 256$  input ports and 256 output ports.

11) It performs the following arithmetic and logical operations.

- 8 bit, 16 bit binary addition

- 2 digit BCD addition

- 8 bit <u>binary subtraction</u>

- logical AND, OR, EXOR

- complement and shift operations.

12) 8085 microprocessor has five hardware interrupts: TRAP, RST 5.5, RST 6.5, RST 7.5, INTR

13) The hardware interrupt capability of 8085 microprocessor can be increased by providing external hardware.

14) 8085 microprocessor has capability to share its bus with external bus controller (<u>direct memory</u> <u>access</u> controller); for transferring large amount of data from memory to I/O and vice versa.

15) 8085 microprocessor provides one accumulator, one flag register, 6 general purpose registers and two special purpose registers.

16) It provides status for advanced control signals. (Advanced control signals are used in large systems).

17) 8085 microprocessor can be used to implement three chip microcomputer (8085, 8155, 8355)

18) 8085 microprocessor provides two serial I/O lines which are SOD and SID; it means, serial peripherals can be interfaced with 8085 microprocessor directly.

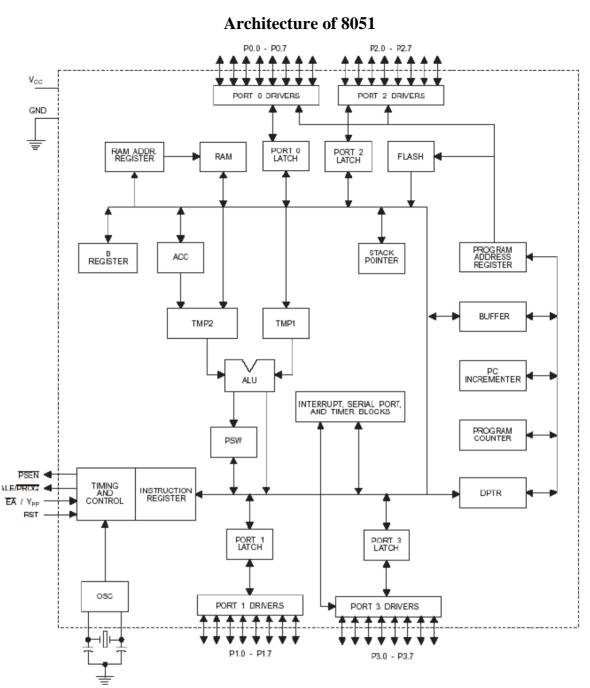

2) Explain with neat sketch about the architecture of 8085.(OR) Explain the architecture of 8085 microprocessor with block diagram. (Nov/Dec-09, April/May-11, May/June-12, Nov/Dec-15, April/May-15, Nov/Dec -16)

#### Architecture of 8085 microprocessor

8085 consists of various units and each unit performs its own functions. The various units of a microprocessor are listed below

- 1. Accumulator

- 2. Arithmetic and logic Unit

- 3. General purpose register

- 4. Program counter

- 5. Stack pointer

- 6. Temporary register

- 7. Flags

- 8. Instruction register and Decoder

- 9. Timing and Control unit

- 10. Interrupt control

- 11. Serial Input/output control

- 12. Address buffer and Address-Data buffer

#### 1) Accumulator

- Accumulator is nothing but a register which can hold 8-bit data. Accumulator aids in storing two quantities.

- > The data to be processed by <u>arithmetic and logic unit</u> is stored in accumulator.

- > It also stores the result of the operation carried out by the Arithmetic and Logic unit.

- > The accumulator is also called an <u>8-bit register</u>.

- > The accumulator is connected to <u>Internal Data bus and ALU</u> (arithmetic and logic unit).

- > The accumulator can be used to **send or receive data** from the Internal Data bus.

#### 2) Arithmetic and Logic Unit

There is always a need to perform arithmetic operations like +, -, \*, / and to perform logical operations like AND, OR, NOT etc. So there is a necessity for creating a separate unit which can perform such types of operations. These operations are performed by the Arithmetic and Logic Unit (ALU). ALU performs these operations on 8-bit data.

But these operations cannot be performed unless we have an input (or) data on which the desired operation is to be performed. So from where do these inputs reach the ALU? For this purpose accumulator is used. ALU gets its Input from accumulator and temporary register. After processing the necessary operations, the result is stored back in accumulator.

#### 3) General Purpose Registers

Apart from accumulator **8085 consists of six special types of registers called General Purpose Registers.** These general purpose registers are used to hold data like any other registers. The general purpose registers in 8085 processors are <u>B, C, D, E, H and L</u>. Each register can **hold 8-bit data**. Apart from the above function these registers can also be used to work in **pairs to hold 16-bit data**. They can work in pairs such as **B-C, D-E and H-L** to store 16-bit data. The H-L pair works as a memory pointer. A memory pointer holds the address of a particular memory location. They can store 16-bit address as they work in pair.

#### 4) Program Counter and 5) Stack Pointer

Program counter is a **special purpose register**. Consider that an instruction is being executed by processor. As soon as the ALU finished executing the instruction, the processor looks for the next instruction to be executed. So, there is a necessity for holding the address of the next instruction to be executed in order to save time.

This is taken care by the program counter. A program counter stores the address of the next instruction to be executed. In other words the program counter keeps track of the memory address of the instructions that are being executed by the microprocessor and the memory address of the next instruction that is going to be executed.

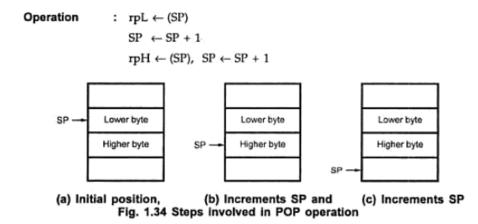

Program counter is a 16-bit register. **Stack pointer** is also a 16-bit register which is used as a memory pointer. A stack is nothing but the portion of RAM (Random access memory). **So does that mean the stack pointer points to portion of RAM? Yes**. Stack pointer maintains the address of the last byte that is entered into stack. Each time when the data is loaded into stack, Stack pointer gets decremented. Conversely it is incremented when data is retrieved from stack.

#### 6) Temporary Register:

As the name suggests this register acts as a temporary memory during the arithmetic and logical operations. Unlike other registers, this temporary register can only be accessed by the microprocessor and it is completely inaccessible to programmers. Temporary register is an 8-bit register. In the next article let us discuss about the FLAGS.

#### 7) Flags(Nov/Dec 2017)

Flags are nothing but a group of individual Flip-flops. The flags are mainly associated with arithmetic and logic operations. The flags will show either a logical (0 or 1) (i.e.) a set or reset depending on the data conditions in accumulator or various other registers. A flag is actually a latch which can hold some bits of information. It alerts the processor that some event has taken place.

#### UNIT-1 EE6502 MICROPROCESSORS AND MICROCONTROLLERS

Why are they called flags?

The possible solution is from the small flags which are found on the mail boxes in America. The small flag indicates that there is a mail in the mail box. Similarly this denotes that an event has occurred in the processor. Intel processors have a set of 5 flags.

- ✤ Carry flag

- ✤ Parity flag

- ✤ Auxiliary carry flag

- ✤ Zero flag

- ✤ Sign flag

Consider two binary numbers. For example: 1100 0000 & 1000 0000

When we add the above two numbers, a carry is generated in the most significant bit. The number in the extreme right is least significant bit, while the number in extreme left is most significant bit. So a ninth bit is generated due to the carry. So how to accommodate 9th bit in an 8 bit register? For this purpose the Carry flag is used. The carry flag is set whenever a carry is

generated and reset whenever there is no carry. But there is an auxiliary carry flag? What is the difference between the carry flag and auxiliary carry flag?

Let's discuss with an example. Consider the two numbers given below

0000 0100, 0000 0101.

When we add both the numbers a carry is generated in the third bit from the least significant bit. This sets the auxiliary carry f lag. When there is no carry, the auxiliary carry flag is reset. So whenever there is a carry in the most significant bit Carry flag is set. While an auxiliary carry flag is set only when a carry is generated in bits other than the most significant bit. Parity checks whether its even or add parity. This flag returns a 0 if it is odd parity and returns a 1 if it is an even parity. Sometimes they are also called as parity bit which is used to check errors while data transmission is carried out. Zero flag shows whether the output of the operation is 0 or not. If the value of Zero flag is 0 then the result of operation is not zero. If it is zero the flag returns value

1. Sign flag shows whether the output of operation has positive sign or negative sign. A value 0 is returned for positive sign and 1 is returned for negative sign. Instruction Register and Decoder Instruction register is 8-bit register just like every other register of microprocessor. Consider an instruction.

2. The instruction may be anything like adding two data's, moving a data, copying a data etc. When such an instruction is fetched from memory, it is directed to Instruction register. So the instruction registers are specifically to store the instructions that are fetched from memory. There is an Instruction decoder which decodes the information present in the Instruction register for further processing.

#### 8) Timing and Control Unit

Timing and control unit is a very important unit as it synchronizes the registers and flow of data through various registers and other units. This unit consists of an oscillator and controller sequencer which sends control signals needed for internal and external control of data and other units. The oscillator generates two-phase clock signals which aids in synchronizing all the registers of 8085 microprocessor.

Signals that are associated with Timing and control unit are: Control Signals: READY, ALE, Status Signals: S0, S1, IO/ M<sup>-</sup> DMA Signals: HOLD, HLDA RESET Signals: RESET IN, RESET OUT

#### 9) Interrupt Control

As the name suggests this control interrupts a process. Consider that a microprocessor is executing the main program. Now whenever the interrupt signal is enabled or requested the microprocessor shifts the control from main program to process the incoming request and after the completion of request, the control goes back to the main program. For example an Input/output device may send an interrupt signal to notify that the data is ready for input. The microprocessor temporarily stops the execution of main program and transfers control to I/O device. After collecting the input data the control is transferred back to main program.

Interrupt signals present in 8085 are:

- 1. INTR

- 2. RST 7.5

- 3. RST 6.5

- 4. RST 5.5

- 5. TRAP

Of the above four interrupts TRAP is a NON-MASKABLE interrupt control and other three are maskable interrupts. A non-maskable interrupt is an interrupt which is given the highest priority in the order of interrupts. Suppose you want an instruction to be processed immediately, then you can give the instruction as a non-maskable interrupt. Further the non-maskable interrupt cannot be disabled by programmer at any point of time.Whereas the maskable interrupts can be disabled and enabled using EI and DI instructions. Among the maskable interrupts RST 7.5 is given the highest priority above RST 6.5 and least priority is given to INTR.

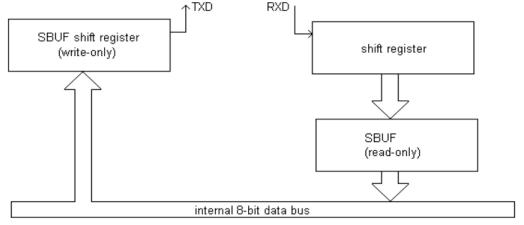

#### 10) Serial I/O control

The input and output of serial data can be carried out using 2 instructions in 8085.

- SID-Serial Input Data

- SOD-Serial Output Data

Two more instructions are used to perform serial-parallel conversion needed for serial I/O devices. SIM RIM

#### 11) Address buffer and Address-Data buffer

The contents of the stack pointer and program counter are loaded into the address buffer and address-data buffer. These buffers are then used to drive the external address bus and address-data bus. As the memory and I/O chips are connected to these buses, the CPU can exchange desired data to the memory and I/O chips. The address-data buffer is not only connected to the external data bus but also to the internal data bus which consists of 8 -bits. The address data buffer can both send and receive data from internal data bus. Address bus and Data bus:

We know that 8085 is an 8-bit microprocessor. So the data bus present in the microprocessor is also 8-bits wide. So 8-bits of data can be transmitted from or to the microprocessor. But 8085 processor requires 16 bit address bus as the memory addresses are 16-bit wide. The 8 most significant bits of the address are transmitted with the help of address bus and the 8 least significant bits are transmitted with the help of multiplexed address/data bus. The eight bit data bus is multiplexed with the eight least significant bits of address bus.

#### 12) Address Bus/Data Bus:

The address/data bus is time multiplexed. This means for few microseconds, the 8 least significant bits of address are generated, while for next few seconds the same pin generates the data. This is called <u>Time multiplexing</u>. But there are situations where there is a need to transmit both data and address simultaneously. For this purpose a signal called ALE (address latch enable) is used. ALE signal holds the obtained address in its latch for a long time until the data

is obtained and so when the microprocessor sends the data next time the address is also available at the output latch. This technique is called Address/Data demultiplexing.

#### 3) Register structure of 8085.Explain the registers of 8085 microprocessor[ Apr/may-17]

#### The 8085 registers are classified as:

- 1. General Purpose Registers

- 2. Temporary Registers a) Temporary data register b) W and Z registers

- 3. Special Purpose Registers a) Accumulator b) Flag registers c) Instruction register

- 4. Sixteen Bit Registers a) Program Counter (PC) b) Stack Pointer (SP)

#### 1. General Purpose Registers

B, C, D, E, H and L are 8-bit general purpose registers can be used as a separate 8-bit registers or as 16-bit register pairs, BC, DE, and HL. When used in register pair mode, the high order byte resides in the first register (i.e. in B when BC is used as a register pair) and the low order

byte in the second (i.e. in C when BC is used as a register pair).HL pair also functions as a data pointer or memory pointer. These are also called scratchpad registers, as user can store data in them.

#### 2. Temporary Registers

a) **Temporary Data Register:** The ALU has two inputs. One input is supplied by the accumulator and other from temporary data register. The programmer cannot access this temporary data register. However, it is internally used for execution of most of the arithmetic and logical instructions.

b) **W and Z Registers**: W and Z registers are temporary registers. These registers are used to hold 8-bit data during execution of some instructions. These registers are not available for programmer, since 8085 uses them internally.

#### 3) Special Purpose Registers

#### a) Register A (Accumulator):

It is a tri-state eight bit register. It is extensively used in arithmetic, logic, load, and store operations, as well as in, input/output (I/O) operations.

Most of the times the result of arithmetic and logical operations is stored in the register A. Hence it is also identified as accumulator.

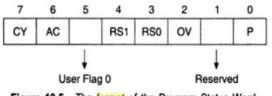

**b**) **Flag Register**: It is an 8-bit register, in which five of the bits carry significant information in the form of flags: S (Sign flag), Z (Zero flag), AC (Auxiliary Carry flag), P (Parity flag), and CY (Carry flag), as shown in Fig. 1.3.

| D7 | D <sub>6</sub> | $D_5$ | D <sub>4</sub> | D <sub>3</sub> | D <sub>2</sub> | D <sub>1</sub> | DO |  |

|----|----------------|-------|----------------|----------------|----------------|----------------|----|--|

| S  | z              | x     | AC             | x              | Р              | ×              | CY |  |

#### S-Sign flag:

After the execution of arithmetic or logical operations, if bit D7 of the result is 1, the sign flag is <u>set</u>. In a given byte if D7 is 1, the number will be viewed as negative number. if D7 is 0, the number will be considered as positive number.

**Z-Zero flag:** The zero flag sets if the result of operation in ALU is zero and flag resets if result is non zero.

**AC-Auxiliary Carry flag:** This flag is set if there is an overflow out of bit 3 i.e., carry from lower nibble to higher nibble (D3 bit to D4 bit). This flag is used for BCD operations and it is not available for the programmer.

**P-Parity flag:** After an arithmetic or logical operation if the result has an even number of ones, i.e. even parity, the flag is set. If the parity is odd, flag is reset.

**CY-Carry flag:** This flag is set if there is an overflow out of bit 7. The carry flag also serves as a borrow flag for subtraction.

c) **Instruction Register:** In a typical processor operation, the processor first fetches the opcode of instruction from memory. The CPU stores this opcode in a register called the instruction register.

#### 4. Sixteen Bit Registers

a) **Program Counter (PC):** Program is a sequence of instructions. Microprocessor fetches these instructions from the memory and executes them sequentially. The program counter is a special purpose register which, at a given time, stores the address of the next instruction to be fetched. Program Counter acts as a pointer to the next instruction.

How processor increments program counter depends on the nature of the instruction

**b**) **Stack Pointer (SP):** The stack is a reserved area of the memory in the RAM where temporary information may be stored. A 16-bit stack pointer is used to hold the address of the most recent stack entry.

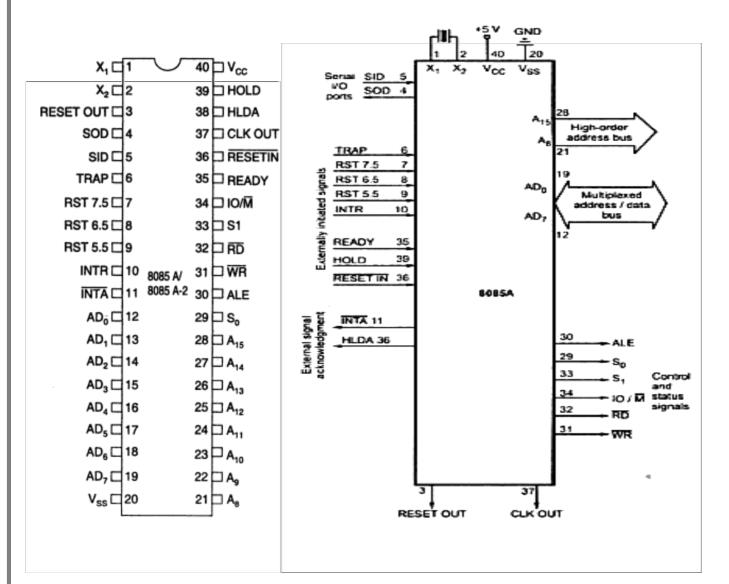

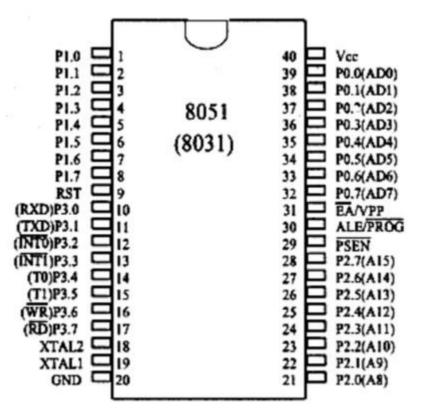

# 4) Draw the pin configuration (signals) of 8085 microprocessor and explain it in detail. (May/June-12)(Nov/Dec-14(Or) With Pin diagram explain 8085 microprocessor.(Apr/May-17)[Apr/May 2018]

The 8085 microprocessor is available on a 40 pin dual in line package (DIP). The pin configuration is shown

- a. Power supply and frequency signals.

- b. Data bus and address bus.

- c. Control bus.

- d. Interrupt signals.

- e. Serial I/O signals.

- f. DMA signals.

- g. Reset signals.

#### a) Power Supply and Frequency Signals

- **VCC**: It requires a single +5 V power supply. i) ii)

- VSS: Ground reference.

X1 and x2: A tuned circuit like LC, RC or crystal is connected at these TWO pins. iii) The internal clock generator divides oscillator frequency by 2, therefore, to operate a system at 3 MHz, the crystal of tuned circuit must have a frequency of 6 MHz

CLK OUT: This signal is used as a system clock for other devices. Its frequency is iv) half the oscillator frequency.

#### b) Data Bus and Address Bus

A) AD<sub>0</sub> to AD<sub>7</sub>: The 8 bit data bus ( $D_0$ –D7) is multiplexed with the lower half (A0–A7) of the 16 bit address bus.

**B)** A8 to A15: The upper half of the 16 bit address appears on the address lines A8to A15.

#### C ) Control and Status Signals

Control Pins – RD, WR These are active low Read & Write pins

Status Pins – ALE, IO/M (active low), S1, S0

ALE (Address Latch Enable)-Used to de-multiplex AD7-AD0 IO/M – Used to select I/O or Memory operation S1,S0 – Denote the status of data on data bus

#### d) Interrupt Signals

The 8085 has five hardware interrupt signals. RST 5.5, RST 6.5, RST 7.5, TRAP and INTR. The microprocessor recognizes interrupt requests on these lines at the end of the current instruction execution.

The (Interrupt Acknowledge) signal is **used** to indicate that the processor has acknowledged an INTR interrupt.

#### e) Serial I/O Signals

A) SID (Serial Input Data): This input signal is used to accept serial data bit by bit from the external device.

**B) SOD** (**Serial O/P Data**): This is an output signal which enables the transmission of serial data bit by bit to the external device.

#### f) DMA Signal

**HOLD: This** signal indicates that **another master is** requesting for the **use** of address bus, data bus and control bus.

HLDA: This active high signal is used to acknowledge HOLD request.

#### g) Reset Signals

A low on this pin

- 1. Internal sets the program counter to zero (0000H).

- 2. Resets the interrupt enable and HLDA flip-flops.

- 3. Tri-states the data bus, address bus and control bus (Note: Only during RESET is active).

- 4. Affects the contents of processor's registers randomly.

**RESET OUT:** This active high signal indicates that processor is being reset. This signal is synchronized to the processor clock and it can be used to reset other devices connected in the system.

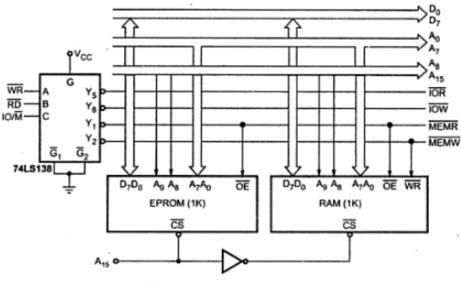

### 5. Explain Memory interfacing in 8085 microprocessor (Or) Draw the interfacing diagram to interface with 8085with 2 KB RAM and 4 KB EPROM (Nov/Dec-16, Apr/May - 17)

#### The memory interfacing requires to:

- Select the chip

- Identify the register

- Enable the appropriate buffer.

Microprocessor system includes memory devices and I/O devices. It is important to note that microprocessor can communicate (read/write) with only one device at a time, since the data, address and control buses are common for all the devices. In order to communicate with memory or I/O devices, it is necessary to decode the address from the microprocessor. Due to this each device (memory or I/O) can be accessed independently. The following section describes common address decoding techniques.

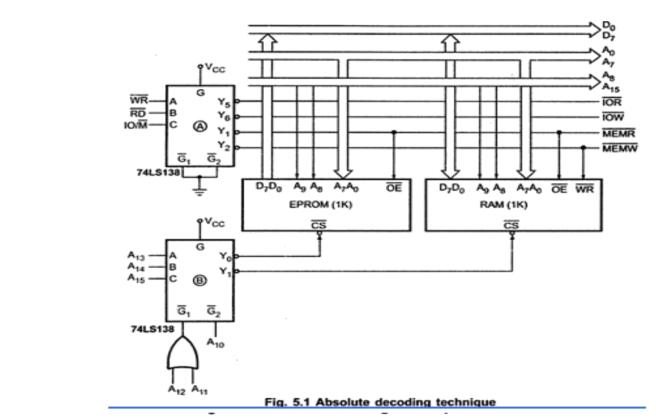

#### **Address Decoding Techniques:**

- Absolute decoding/Full Decoding

- Linear decoding/Partial Decoding

#### Absolute decoding

In absolute decoding technique, all the higher address lines are decoded to select the memory chip, and the memory chip is selected only for the specified logic levels on this high-order address lines; no other logic levels can select the chip. Fig. 5.1 shows the memory interface with absolute decoding. This addressing technique is normally used in large memory systems.

#### Memory Map :

| Memory ICs                   | A <sub>15</sub> | A <sub>14</sub> | A <sub>13</sub> | A12 | A11 | A <sub>10</sub> | Ag | A <sub>8</sub> | A7 | A <sub>6</sub> | Α5 | A4 | A <sub>3</sub> | A <sub>2</sub> | A1 | A <sub>0</sub> | Address |

|------------------------------|-----------------|-----------------|-----------------|-----|-----|-----------------|----|----------------|----|----------------|----|----|----------------|----------------|----|----------------|---------|

| Starting address of<br>EPROM | 0               | 0               | 0               | 0   | 0   | 0               | 0  | 0              | 0  | Ó              | 0  | 0  | 0              | 0              | 0  | 0              | 0000H   |

| End address of<br>EPROM      | 0               | 0               | 0               | 0   | 0   | 0               | 1  | 1              | 1  | 1              | 1  | 1  | 1              | 1              | 1  | 1              | 03FFH   |

| Starting address of<br>RAM   | 0               | 0               | 1               | 0   | 0   | 0               | 0  | 0              | 0  | 0              | 0  | 0  | 0              | 0              | 0  | 0              | 2000H   |

| End address of RAM           | 0               | 0               | 1               | 0   | 0   | 0               | 1  | 1              | 1  | 1              | 1  | 1  | 1              | 1              | 1  | 1              | 23FFH   |

#### Table 5.1

#### Linear decoding

In small systems, hardware for the decoding logic can be eliminated by using individual highorder address lines to select memory chips. This is referred to as linear decoding. Fig. 5.2 shows the addressing of RAM with linear decoding technique. This technique is also called partial decoding. It reduces the cost of decoding circuit, but it has a drawback of multiple addresses (shadow addresses).

#### Memory Map :

| Memory ICs                | A <sub>15</sub> | A <sub>14</sub> | A <sub>13</sub> | A <sub>12</sub> | A <sub>11</sub> | A <sub>10</sub> | A9 | A <sub>8</sub> | A7  | A <sub>6</sub> | Α5 | A4 | A3 | A <sub>2</sub> | A1 | Ao | Address |

|---------------------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|----|----------------|-----|----------------|----|----|----|----------------|----|----|---------|

| Starting address of EPROM | 0               | <b>x</b> `      | x               | x               | х               | x               | 0  | 0              | . 0 | 0              | 0  | 0  | 0  | 0              | 0  | 0  | 0000H   |

| End address of EPROM      | 0               | ·χ              | x               | x               | . <b>X</b> .    | x               | 1  | 1              | 1   | 1              | 1  | 1  | 1  | 1              | 1  | 1  | 03FFH   |

| Starting address of RAM   | 1               | x               | x               | x               | x               | x               | 0  | 0              | 0   | 0              | 0  | ·0 | 0  | 0              | 0  | 0  | 8000H   |

| End address of RAM        | 1               | x               | x               | x               | х               | x               | 1  | 1              | 1   | 1              | 1  | 1  | 1  | 1              | 1  | 1  | 83FFH   |

#### Table 5.2

| Full Address Decoding                                                       | Partial Address Decoding                                                                                       |

|-----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| 1. All higher address lines are decoded to select the memory or I/O device. | <ol> <li>Few higher address lines are decoded to select the<br/>memory or I/O device.</li> </ol>               |

| 2. More hardware is required to design decoding logic.                      | <ol> <li>Hardware required to design decoding logic is less<br/>and sometimes it can be eliminated.</li> </ol> |

| 3. Higher cost for decoding circuit.                                        | 3. Less cost for decoding circuit.                                                                             |

| 4. No multiple addresses.                                                   | <ol> <li>It has a disadvantage of multiple addresses (shadow<br/>addresses).</li> </ol>                        |

| 5. Used in large systems.                                                   | 5. Used in small systems.                                                                                      |

Table 5.3

Fig. 5.2 Linear decoding

Fig. 5.2 shows the addressing of RAM with linear decoding technique. A15 address line is directly connected to the chip select signal of EPROM and after inversion it is connected to the

chip select signal of the RAM. Therefore, when the status of  $A_15$  line is 'zero', EPROM gets selected and when the status of A15 line is 'one' RAM gets selected. The status of the other address lines is not considered, since those address lines are not used for generation of chip select signals.

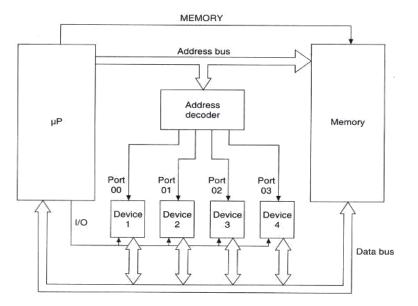

#### 6.Explain I/O Interfacing Techniques of microprocessor 8085

#### I/O Mapped I/O Interface

The I/O devices are identified by port numbers, and memory locations are identified by addresses. The memory read/write operations and I/O read/write operations are performed by different software instructions.

Whether the read/write operations are being performed on memory or I/O, or in other words whether the information on address and data lines is meant for a memory location or an I/O device—this identification is done by separate signals.

Thus, when read from an I/O device instruction is executed, the I/O signal is ON and the address on the address bus is decoded as the port number and an I/O device is selected.

#### I/O Mapped I/O Interface

In case of read/write from memory, the MEMORY signal is ON and a particular location of memory is selected. Because of separate memory and I/O signals, there is no confusion between device address (i.e. port number) and memory address. This is called I/O mapped I/O interface since I/O devices are treated separately from memory.

#### **Memory Mapped I/O Interface**

Consider the case except that the signals I/O and MEMORY are not present. Now when a read memory instruction is executed, there is no MEMORY signal to indicate that the address bus contains the memory location address.

If this memory location address is the same as that of a port number of an I/O device, an I/O device will also get selected together with the memory read operation being performed. Thus, there will be confusion between memory location and I/O device having the same address and port number.

To read from device 1 (Port no. 00) memory location 00 will also get selected. However, if some memory locations is satisfied for the sake of I/O devices, this problem would not arise. It means that the I/O addresses (port numbers) and the memory addresses will not be the same. If the memory starts from address 04 onwards, then there would not be any problem.

The memory read/write instructions are quite versatile and powerful in general. If a microprocessor has more than one register apart from ACC (the 8085 has six registers other than ACC), then the memory operations can be performed using any of these registers. These instructions automatically become valid for I/O devices if connected in this fashion. The I/O read/write instructions in I/O-mapped I/O, normally require the transfer from an I/O port to accumulator. The same data is then subsequently transferred to the other register, thus wasting one instruction.

The memory read/write instructions employ various powerful addressing modes like indexed, indirect, base register addressing, etc. which is not true in the case of I/O read/write instructions. Thus, more compact and more efficient handling of I/O devices can be achieved if they are interfaced to microprocessor in this way. Since an I/O device is treated as memory location (identified by memory address), this interface is called memory mapped I/O.

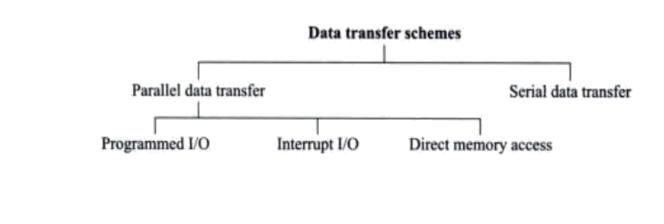

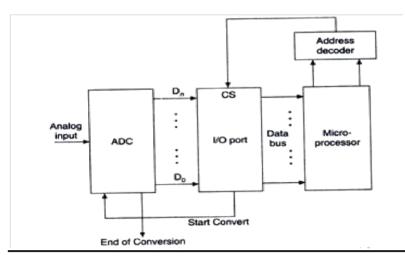

#### 7. Explain in brief about Data Transfer Schemes of 8085.

**Data transfer** schemes depend heavily on the environment (on-line or off-line processing), type of I/O device (capable of parallel or serial data transfer, synchronous or asynchronous) and the application. Data transfer schemes may be categorized as shown below.

#### 7.1 Parallel Data Transfer

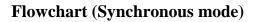

#### 7.1.1 Programmed I/0

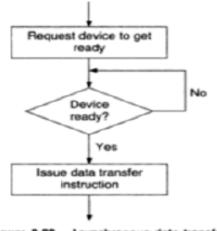

In programmed I/O, the data transfer is controlled by the user program being executed. Depending on the type of the device, data transfer may be synchronous or asynchronous. Synchronous data transfer is used when the I/O device matches in speed with the microprocessor.

The microprocessor issues the read/write instruction addressing the *device* whenever data transfer is required. The actual data transfer takes place in one clock *cycle*.

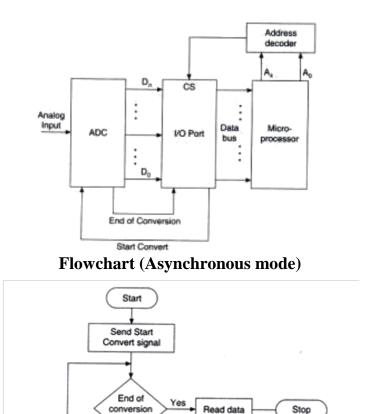

When the I/O device speed and the microprocessor speed do not match, i.e. when the I/O device is slower than the microprocessor, asynchronous data transfer is used. In this mode of data transfer, the microprocessor checks the status of the device. If the device is not ready, the microprocessor continuously checks the status of the device till it becomes ready. The data transfer instruction is then issued by the microprocessor (Figure 2.20).

Figure 2.20 Asynchronous data transfer.

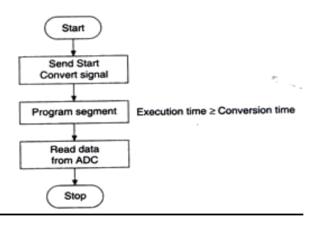

#### 7.1.2 INTERRUPT I/O

The data transfer scheme in Figure 2.19 is quite inefficient, since the microprocessor is kept busy for the slower I/O device. The remedy to this problem is to allow the microprocessor to do its job when the device is getting ready and when the device is ready, the microprocessor can transfer the data. This can be achieved through interrupt.

When the interrupt signal is present, it should suspend the current job. The current status of the suspended job should be stored so that the microprocessor can restart the suspended job from the same point. The stack is *used* to store the status of the suspended job.

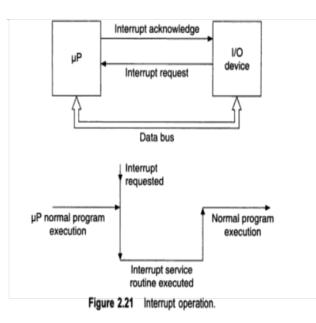

The microprocessor services the interrupt request by executing an Interrupt Service Routine. The interrupt operation is explained in Figure 2.21.

Following is the operation sequence for interrupt operation.

- (a) Normal program execution by microprocessor.

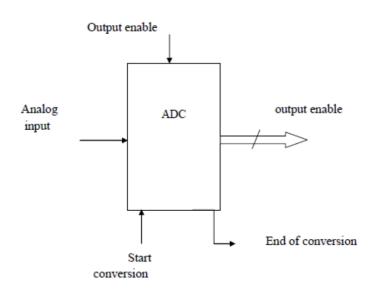

- (b) The microprocessor initiates the device through a code/signal (e.g. start convert signal to initiate ADC conversion).

- (c) The device when ready to send the data sends an interrupt signal on one of the interrupt pins.

- (d) The microprocessor checks the validity of the interrupt request by checking whether

- The interrupt system is enabled.

- The particular interrupt is not disabled.

- Any higher priority interrupt is not pending or being processed.

(e) If an interrupt request is valid, the microprocessor

- Completes the current instruction execution.

- Saves the Status Register and Program Counter (PC) in stack.

- Issues the interrupt acknowledgement signal.

• Determines the address of the interrupt servicing routine and stores the starting address in PC. The program thus branches to Interrupt Servicing Routine.

The last instruction of Interrupt Servicing Routine is 'Return'. When this instruction is executed, the PC and the Status Register are loaded back from stack. Thus normal program execution is resumed.

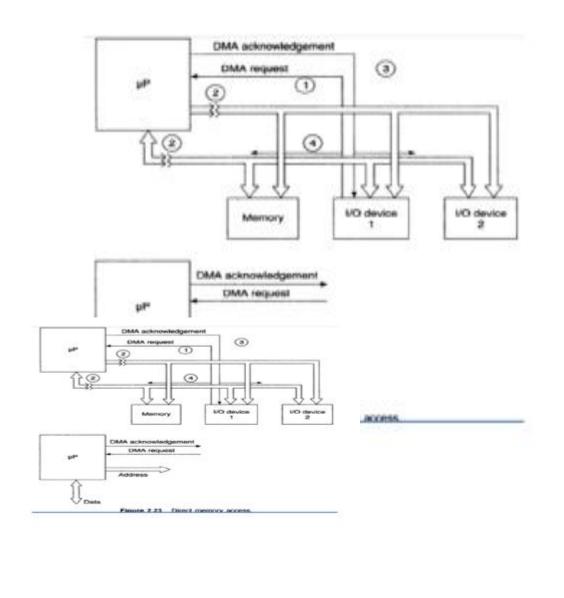

#### 7.1.3 Direct memory access

In programmed I/O and interrupt I/O, data is transferred to the memory through the accumulator. This process is quite uneconomical for bulk data transfer, when the I/O device matches the speed of the microprocessor. In such cases the device is allowed to transfer the data directly to memory, bypassing the microprocessor.

#### Following is the operation sequence in case of Direct Memory Access.

- 1. The microprocessor checks for DMA request signal once in each machine cycle.

- 2. The I/0 device sends the signal on DMA Request pin.

- 3. The microprocessor tristates the address, data and control buses.

- 4. The microprocessor sends the acknowledgement signal to the I/O device on DMA Acknowledgement pin.

- 5. The I/O device uses the bus system to perform the data transfer operation on memory.

- 6. On completion of data transfer, the I/O device withdraws the DMA request signal.

- 7. The microprocessor continuously checks the DMA request signal. When the signal is withdrawn, the microprocessor regains the control of buses and resumes normal operation.

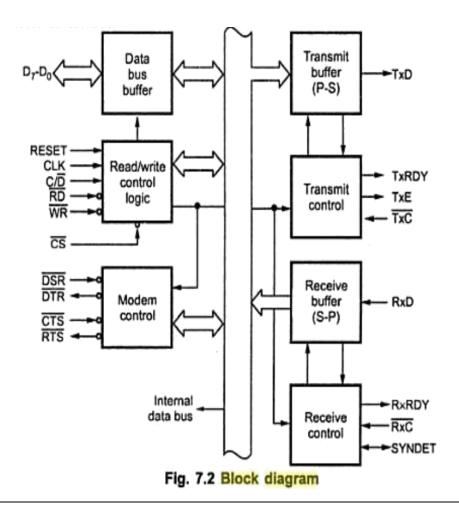

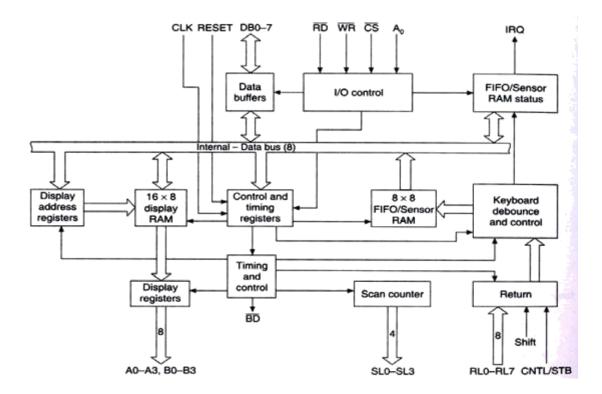

#### 7.2 Serial Data Transfer

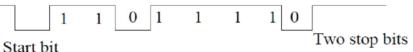

Some devices like CRI receive and transmit data in serial mode. The data transfer between two processors will be in serial mode. The data is transferred bit by bit on a single line. This minimizes the number of interconnecting wires.

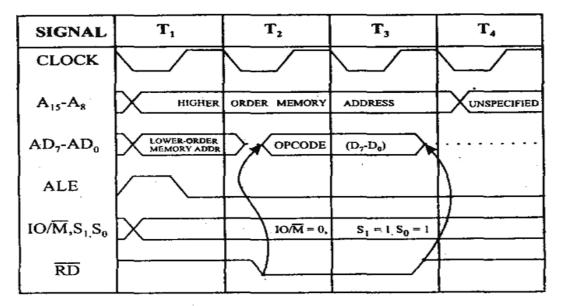

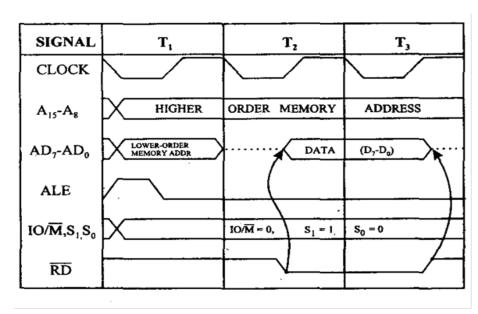

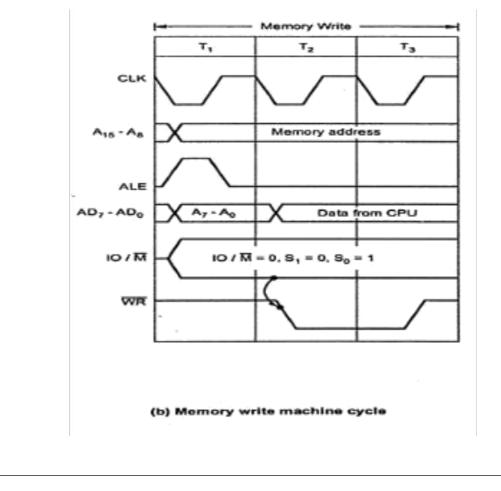

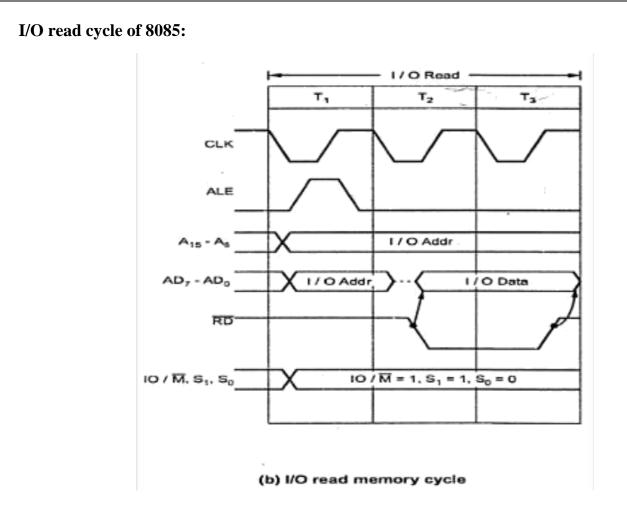

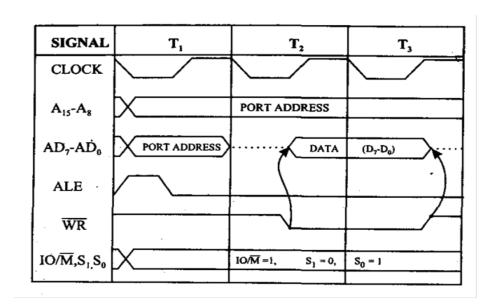

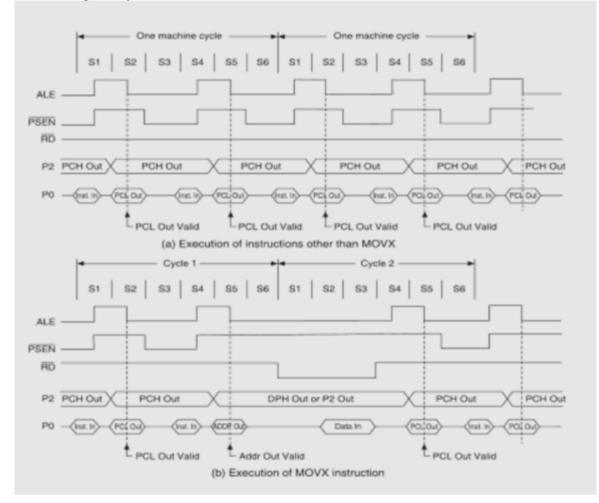

## 8. Draw the timing diagram for opcode fetch, Memory Read & Write, I/O Read & Write of 8085 processor. (*Nov/Dec-09, April/May-11, May/June-12*)(*Nov/Dec-14*)(*Nov/Dec-15*)(*Or*) Draw the timing diagram for I/O read & write Machine Cycles. (Nov 2016)[Apr/May 2018]

Timing Diagram is a graphical representation. It represents the execution time taken by each instruction in a graphical format. The execution time is represented in T-states.

#### **Instruction Cycle:**

The time required to execute an instruction is called instruction cycle.

#### Machine Cycle:

The time required to access the memory or input/output devices is called machine cycle.

#### **T-State**:

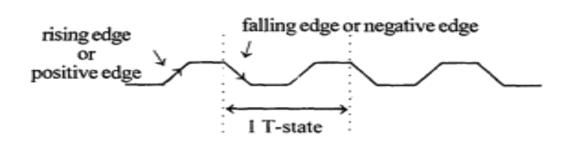

- The machine cycle and instruction cycle takes multiple clock periods.

- A portion of an operation carried out in one system clock period is called as T-state.

#### MACHINE CYCLES OF 8085:

The 8085 microprocessor has 5 (seven) basic machine cycles. They are

- 1. Opcode fetch cycle (4T)

- 2. Memory read cycle (3 T)

- 3. Memory write cycle (3 T)

- 4. I/O read cycle (3 T)

- 5. I/O write cycle (3 T)

- 6. Interrupt acknowledge cycle

- 7. Bus idle cycle

Each instruction of the 8085 processor consists of one to five machine cycles, i.e., when the 8085 processor executes an instruction, it will execute some of the machine cycles in a specific order.

The processor takes a definite time to execute the machine cycles. The time taken by the processor to execute a machine cycle is expressed in T-states.

One T-state is equal to the time period of the internal clock signal of the processor. The Tstate starts at the falling edge of a clock.

Time period, T = 1/f; where  $f = Internal \ clock \ frequency$

#### **Opcode fetch machine cycle of 8085:**

- Each instruction of the processor has one byte opcode.

- The opcodes are stored in memory. So, the processor executes the opcode fetch machine cycle to fetch the opcode from memory.

- Hence, every instruction starts with opcode fetch machine cycle.

- The time taken by the processor to execute the opcode fetch cycle is 4T.

- In this time, the first, 3 T-states are used for fetching the opcode from memory and the remaining T-states are used for internal operations by the processor.

#### Memory read machine cycle of 8085:

- The memory read machine cycle is executed by the processor to read a data byte from memory.

- The processor takes 3T states to execute this cycle.

- The instructions which have more than one byte word size will use the machine cycle after the opcode fetch machine cycle.

Memory write machine cycle of 8085:

The 8085 executes the memory write *cycle* to store the data into data memory or stack memory. The length of this machine cycle is 3T states ( $T_I - T_3$ ). In this machine cycle, processor places the address on the address lines from the stack pointer or general purpose register pair and through the write process, stores the data into the addressed memory location

The I/O read and I/O write machine cycles are similar to the memory read and memory write machine cycles, respectively, except that the IO/M signal is high for I/O read and I/O write machine cycles. High 10/M signal indicates that it is an I/O operation.

#### I/O write cycle of 8085:

- The I/O write machine cycle is executed by the processor to write a data byte in the I/O port or to a peripheral, which is I/O, mapped in the system.

- The processor takes 3T states to execute this machine cycle.

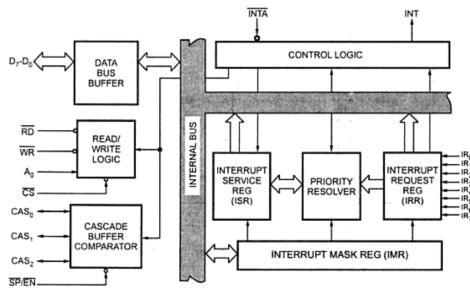

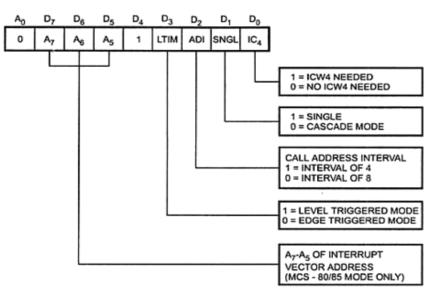

# 9. Explain in detail about the interrupt structure of 8085 processor. (Nov/Dec-09, May/June-12, April/May-15,Nov/Dec-15,Apr/May -17)[Nov/Dec 2017][Apr/May 2018]

Interrupt is signals send by an external device to the processor, to request the processor to perform a particular task or work. Mainly in the microprocessor based system the interrupts are used for data transfer between the peripheral and the microprocessor.

The processor will check the interrupts always at the 2nd T-state of last machine cycle. If there is any interrupt it accept the interrupt and send the INTA (active low) signal to the peripheral.

The vectored address of particular interrupt is stored in program counter. The processor executes an interrupt service routine (ISR) addressed in program counter. It returned to main program by RET instruction.

Types of Interrupts: It supports two types of interrupts.

- Hardware

- Software

#### Software interrupts:

- The software interrupts are program instructions. These instructions are inserted at desired locations in a program.

- The 8085 has eight software interrupts from RST 0 to RST 7. The vector address for these interrupts can be calculated as follows.

- Interrupt number \* 8 = vector address

- For RST 5.5 \* 8 = 40 = 28H

- Vector address for interrupt RST 5 is 0028H

The Table shows the vector addresses of all interrupts.

| Interrupt | Vector address    |

|-----------|-------------------|

| RST 0     | 0000 <sub>H</sub> |

| RST 1     | 0008 <sub>H</sub> |

| RST 2     | 0010 <sub>н</sub> |

| RST 3     | 0018 <sub>н</sub> |

| RST 4     | 0020 <sub>н</sub> |

| RST 5     | 0028 <sub>н</sub> |

| RST 6     | 0030 <sub>н</sub> |

| RST 7     | 0038 <sub>н</sub> |

#### Hardware interrupts:

- An external device initiates the hardware interrupts and placing an appropriate signal at the interrupt pin of the processor.

- If the interrupt is accepted then the processor executes an interrupt service routine.

The 8085 has five hardware interrupts

| (1) TRAP | (2) RST 7.5 | (3) RST 6.5 | (4) RST 5.5 | (5) INTR |

|----------|-------------|-------------|-------------|----------|

|          |             |             |             | · ·      |

| Interrupt | Vector address    |

|-----------|-------------------|

| RST 7.5   | 003C <sub>R</sub> |

| RST 6.5   | 0034 <sub>H</sub> |

| RST 5.5   | 002C <sub>H</sub> |

| TRAP      | 0024 <sub>H</sub> |

#### TRAP:

- This interrupt is a non-maskable interrupt. It is unaffected by any mask or interrupt enable.

- TRAP bas the highest priority and vectored interrupt.

- TRAP interrupt is edge and level triggered. This means hat the TRAP must go high and remain high until it is acknowledged.

- In sudden power failure, it executes a ISR and send the data from main memory to backup memory.

- The signal, which overrides the TRAP, is HOLD signal. (i.e., If the processor receives HOLD and TRAP at the same time then HOLD is recognized first and then TRAP is recognized).

- There are two ways to clear TRAP interrupt.

- 1. By resetting microprocessor (External signal)

- 2. By giving a high TRAP ACKNOWLEDGE (Internal signal)

#### **RST 7.5:**

- The RST 7.5 interrupt is a Maskable interrupt.

- It has the second highest priority.

- It is edge sensitive. ie. Input goes to high and no need to maintain high state until it recognized.

- Maskable interrupt. It is disabled by,

- 1. DI instruction

- 2. System or processor reset.

- 3. After reorganization of interrupt.

- Enabled by EI instruction.

# **RST 6.5 and 5.5:**

- The RST 6.5 and RST 5.5 both are level triggered. . ie. Input goes to high and stay high until it recognized.

- Maskable interrupt. It is disabled by,

- 1. DI, SIM instruction

- 2. System or processor reset.

- 3. After reorganization of interrupt.

- Enabled by EI instruction.

- The RST 6.5 has the third priority whereas RST 5.5 has the fourth priority.

# **INTR:**

- INTR is a maskable interrupt. It is disabled by,

- 1. DI, SIM instruction

- 2. System or processor reset.

- 3. After reorganization of interrupt.

- Enabled by EI instruction.

- Non- vectored interrupt. After receiving INTA (active low) signal, it has to supply the address of ISR.

- It has lowest priority.

- It is a level sensitive interrupts. ie. Input goes to high and it is necessary to maintain high state until it recognized.

The following sequence of events occurs when INTR signal goes high.

1. The 8085 checks the status of INTR signal during execution of each instruction.

2. If INTR signal is high, then 8085 complete its current instruction and sends active low interrupt acknowledge signal, if the interrupt is enabled.

3. In response to the acknowledge signal, external logic places an instruction OPCODE on the data bus. In the case of multi byte instruction, additional interrupt acknowledge machine cycles are generated by the 8085 to transfer the additional bytes into the microprocessor.

4. On receiving the instruction, the 8085 save the address of next instruction on stack and execute received instruction.

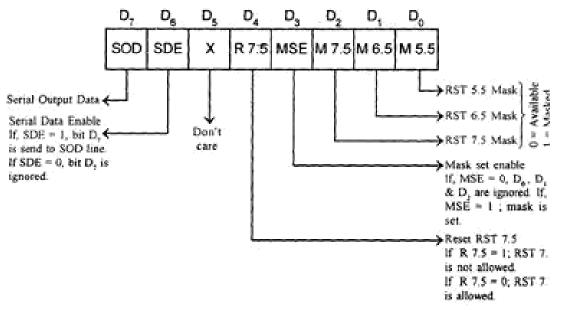

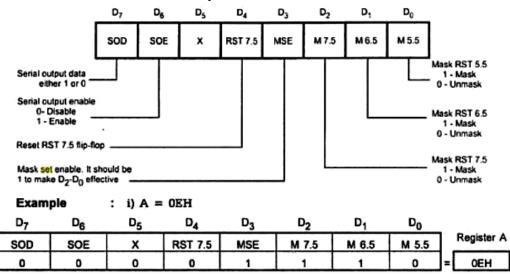

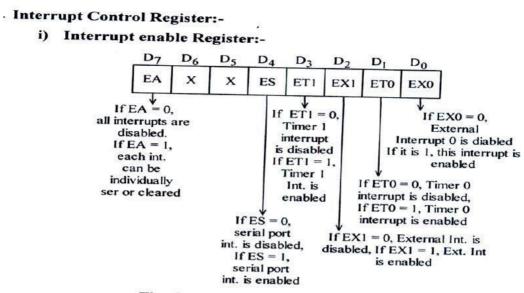

#### SIM and RIM for interrupts:

- The 8085 provide additional masking facility for RST 7.5, RST 6.5 and RST 5.5 using SIM instruction.

- The status of these interrupts can be read by executing RIM instruction.

- The masking or unmasking of RST 7.5, RST 6.5 and RST 5.5 interrupts can be performed by moving an 8-bit data to accumulator and then executing SIM instruction.

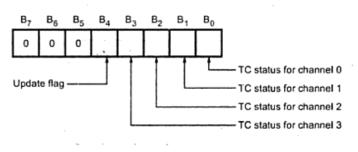

- The format of the 8-bit data is shown below.

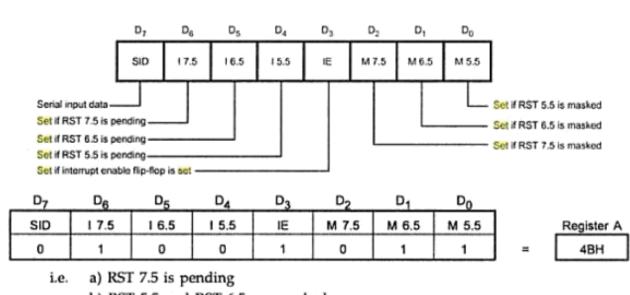

- The status of pending interrupts can be read from accumulator after executing RIM instruction.

- When RIM instruction is executed an 8-bit data is loaded in accumulator, which can be interpreted as shown in fig.

#### 8085 - Demo Programs

Now, let us take a look at some program demonstrations using the above instructions – Adding Two 8-bit Numbers

1) Write a program to add data at 3005H & 3006H memory location and store the result at 3007H memory location.

Problem demo -

(3005H) = 14H (3006H) = 89H

Result -

14H + 89H = 9DH

The program code can be written like this -

LXI H 3005H : "HL points 3005H" MOV A, M : "Getting first operand" INX H : "HL points 3006H" ADD M : "Add second operand" INX H : "HL points 3007H" MOV M, A : "Store result at 3007H" HLT : "Exit program"

Exchanging the Memory Locations

#### 2) Write a program to exchange the data at 5000M& 6000M memory location.

LDA 5000M : "Getting the contents at5000M location into accumulator" MOV B, A : "Save the contents into B register" LDA 6000M : "Getting the contents at 6000M location into accumulator" STA 5000M : "Store the contents of accumulator at address 5000M" MOV A, B : "Get the saved contents back into A register" STA 6000M : "Store the contents of accumulator at address 6000M"

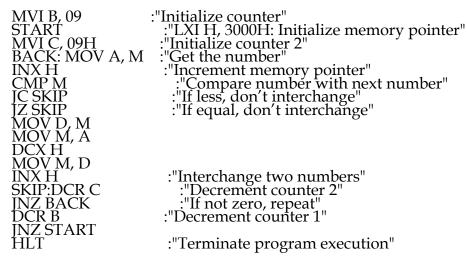

Arrange Numbers in an Ascending Order

# 3) Write a program to arrange first 10 numbers from memory address 3000H in an ascending order.

# Anna University Questions PART-A

1.Specify the size of data, address, and memory word and memory capacity of 8085 microprocessor. (*April/May-2011*)

2. How clock signals are generated in 8085 and what is the frequency of the internal clock?

# (May/June-14)

3. List the control and status signals of 8085 microprocessor and mention its need? (*Nov/Dec-2012*)

4. What is the need for timing diagram? (April/May-15)

5. What is ALE signal and READY signal? (Nov/Dec-09) (Nov/Dec-14)

6. What is the use of ALE? (*Nov/Dec-14*)

7. What is TRAP? (May/June -2012)

- 8. Define Flags of 8085? (Nov/Dec-14)

- 9. Define the functions of parity flag and zero flag in 8085? (May/June-2012)

*10*. What is the use of stack pointer?(**Nov/Dec-15**)

11.Mention the use of ALE(Nov/Dec-15)

12. Write an 8085 assembly program to add two digit BCD numbers in memory locations 5000H and 5001H and store the result in memory location 5002H.(Nov 2016)

13. List out the machine cycles for executing the instruction MVI A,34 H (Nov -16)

14. Why data bus is bi-directional? (Apr/May -17)

15.List out the machine cycles of 8085 microprocessor.(Apr/May -17)

16.what are the flags avaible in 8085 processor?[Nov/Dec 2017]

17.what are the interrupts available in 8085?[Nov/Dec 2017]

18. List the features of Accumulator.[Apr/May 2018]

19. Write the difference between standard I/O and Memory Mapped I/O.[Apr/May 2018]

# PART-B

1. Explain with neat sketch about the hardware architecture of 8085. (*Nov/Dec-09, April/May-11, May/June-12, Nov/Dec-12, April/May-15,Nov/Dec-15,16*) [Nov/Dec 2017]

2. Draw the pin configuration of 8085 microprocessor and explain it in detail. (*May/June-12*) (*May/June-14,17*) (or) Draw the signal present in 8085 microprocessor and explain it in detail ( or) Explain the function 8085 signals? (*Nov/Dec-14*) [*Apr/May 2018*]

3 Distinguish between I/O mapped I/O and Memory mapped I/O of 8085 (*Nov/Dec-09*) (*P.NO* :)

4. Draw the timing diagram for opcode fetch, Memory Read & Write, I/O Read& Write of 8085 processor. (*Nov/Dec-09, April/May-11, May/June-12,Nov/Dec-15*)

5. Explain in detail about the interrupt structure of 8085 processor. (*Nov/Dec-09, May/June-12, April/May-15,Nov/Dec-15)*[*Nov/Dec 2017*][*Apr/May 2018*] 6.Draw and Explain the Flag register of 8085 in brief.[*Nov/Dec 2017*]

| DEP.                         | MAILAM ENG<br>MAILAM<br>ARTMENT OF ELECTRICAL A | GINEERINGCOLLEGE<br>M, 604304<br>ND ELECTRONICS ENGINEERING                                               |

|------------------------------|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| Sub.Code/Sub.Nar             |                                                 | ID MICROCONTROLLERS Year/Sem: III / V                                                                     |

| LINITE IN                    | ne: EE6502 MICROPROCESSORS AN                   | ND MICROCONTROLLERS Year/Senit May                                                                        |

| Instruction<br>manipulation& | RAMMING OF 8085 PROCESS                         | GOR<br>- Assembly language format – Data transfer, data<br>ing: Loop structure with counting & Indexing – |

| Updated Question             |                                                 |                                                                                                           |

| PART-A                       | ns:[Nov/Dec 2017 & Apr/May 20                   | 018]                                                                                                      |

| Q.No.05                      | Page No: 02                                     | (Nov/Dec 2017)                                                                                            |

| Q.No.08                      | Page No: 03                                     | (Nov/Dec 2017)                                                                                            |